# SHENZHEN XINGYUHE CO.,LTD

# **SPECIFICATIONS**

CUSTOMER :

PRODUCT : LCD Module

**SAMPLE CODE** : <u>JGG12864B04</u>

**VER** : 1.0

| Customer Approved | Confirmed | Designer |

|-------------------|-----------|----------|

|                   |           |          |

|                   |           |          |

|                   |           |          |

#### TABLE OF CONTENTS

| GENERAL DESCRIPTION             | 3  |

|---------------------------------|----|

| FEATURS                         | 3  |

| MECHANICAL SPECIFICATION        | 3  |

| MECHANICAL DIMENSION            | 4  |

| PIN DESCRIOTIONS                | 5  |

| MAXIMUM RATINGS                 | 6  |

| ELECTRICAL CHARACTERISTICS      | 6  |

| MODULE FUNCTION DESCRIPTION     | 7  |

| ELECTRO-OPTICAL CHARACTERISTICS | 14 |

#### 1.GENERAL DESCRIPTION

The JGG12864B04 is a 128X64 DOTS MATRIX LCD module which is fabricated by low power COMS technology. It has an STN panel composed of 128 segments and 64 commons. The LCM can be easily accessed by microcontroller via parallel or serial interface.

#### 2.FEATURES

| Display Model       | TRANSMISSIVE and BLUE type             |  |  |  |

|---------------------|----------------------------------------|--|--|--|

|                     | STN Mode LCD                           |  |  |  |

| Display Format      | 128X64 DOTS                            |  |  |  |

| Input Data          | Parallel or serial data input from MPU |  |  |  |

| Multiplexing Ration | 1/65 Duty, 1/9Bias                     |  |  |  |

| Viewing Direction   | 6 O'clock                              |  |  |  |

| DRIVER              | ST7565P                                |  |  |  |

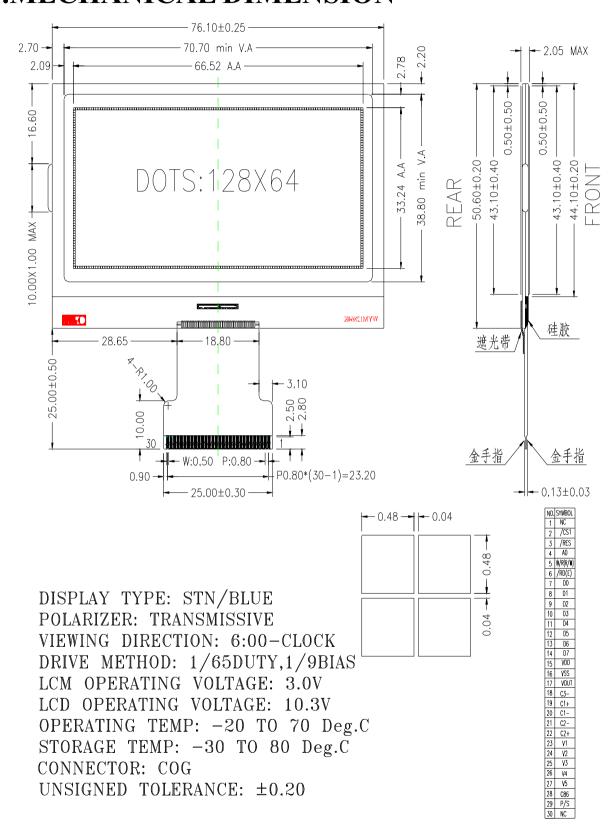

#### 3.MECHANICAL SPECIFICATION

| Item               | Specifications                | Unit |

|--------------------|-------------------------------|------|

| Module Size(W*H*T) | 76.10X (50.60+25.00) X2.05MAX | mm   |

| Viewing Area (W*H) | 70.70X38.80                   | mm   |

| Dot Pitch (W*H)    | 0.52X0.52                     | mm   |

| Dot Size (W*H)     | 0.48X0.48                     | mm   |

| Active Area (W*H)  | 66.52X33.24                   | mm   |

| Number of Dots     | 128X64                        |      |

### 4.MECHANICAL DIMENSION

### 5. PIN DESCRIPTIONS

| PIN    | symbol   | voltage         | FUCTION                                                                                                                                                                                                                                                                                                                                                                 |

|--------|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | NC       |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 2      | /CS1     | I               | This is the chip select signal. When /CS1 = "L", then the chip select becomes active, and data/command I/O is enabled.                                                                                                                                                                                                                                                  |

| 3      | /RES     | I               | When /RES is set to "L," the settings are initialized. The reset operation is performed by the /RES signal level.                                                                                                                                                                                                                                                       |

| 4      | A0       | I               | This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command.  A0 = "H": Indicates that D0 to D7 are display data.  A0 = "L": Indicates that D0 to D7 are control data.                                                                                                                    |

| 5      | W/R(R/W) | _               | <ul> <li>When connected to an 8080 MPU, this is active LOW.</li> <li>(R/W) This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.</li> <li>When connected to a 6800 Series MPU: This is the read/write control signal input terminal. When R/W = "H": Read. When R/W = "L": Write.</li> </ul> |

| 6      | /RD(E)   | 1               | <ul> <li>When connected to an 8080 MPU, this is active LOW.</li> <li>(E) This pin is connected to the /RD signal of the 8080 MPU, and the ST7565P series data bus is in an output status when this signal is "L".</li> <li>When connected to a 6800 Series MPU, this is active HIGH. This is the 6800 Series MPU enable clock input terminal.</li> </ul>                |

| 7      | D0       |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 8      | D1       |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 9      | D2       |                 | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit                                                                                                                                                                                                                                                                                            |

| 10     | D3       | I/O             | standard MPU data bus. When the serial interface is selected (P/S = "L"):                                                                                                                                                                                                                                                                                               |

| 11     | D4       | ",0             | D7 : serial data input (SI) ; D6 : the serial clock input (SCL).  D0 to D5 are set to high impedance.                                                                                                                                                                                                                                                                   |

| 12     | D5       |                 | When the chip select is not active, D0 to D7 are set to high impedance.                                                                                                                                                                                                                                                                                                 |

| 13     | D6       |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 14     | D7       |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 15     | VDD      | Power<br>Supply | Power supply                                                                                                                                                                                                                                                                                                                                                            |

| 16     | VSS      | Power<br>Supply | Ground                                                                                                                                                                                                                                                                                                                                                                  |

| 17     | VOUT     | 0               | DC/DC voltage converter. Connect a capacitor between this terminal and VSS or VDD                                                                                                                                                                                                                                                                                       |

| 18     | C3-      |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 19     | C1+      |                 | DC/DC voltage converter Connect a conscitor between this terminal and                                                                                                                                                                                                                                                                                                   |

| 20 C1- |          | Ο               | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1N terminal.                                                                                                                                                                                                                                                                              |

| 21     | C2-      |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 22     | C2+      |                 |                                                                                                                                                                                                                                                                                                                                                                         |

| 23     | V1       | Power           | power supply liquid crystal drive                                                                                                                                                                                                                                                                                                                                       |

| ** | ************************ |     |        |                                                                                                                 |  |  |  |  |  |

|----|--------------------------|-----|--------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|    | 24                       | V2  | Supply |                                                                                                                 |  |  |  |  |  |

|    | 25                       | V3  |        |                                                                                                                 |  |  |  |  |  |

|    | 26                       | V4  |        |                                                                                                                 |  |  |  |  |  |

|    | 27                       | V5  |        |                                                                                                                 |  |  |  |  |  |

|    | 28                       | C86 | I      | This is the MPU interface switch terminal. C86 = "H": 6800 Series MPU interface. C86 = "L": 8080 MPU interface. |  |  |  |  |  |

|    | 29                       | P/S | I      | This pin configures the interface to be parallel mode or serial mode.                                           |  |  |  |  |  |

|    | 30                       | NC  |        |                                                                                                                 |  |  |  |  |  |

#### 6. MAXIMUM RATINGS

| Item                  | Symbol | Min     | Max     | Unit          |

|-----------------------|--------|---------|---------|---------------|

| C1 V-14               | VDD    | -0.3    | 5.0     | V             |

| Supply Voltage        | Vout   | -0.3    | 18.0    | V             |

| Input Voltage         | Vin    | VSS-0.3 | VDD+0.3 | V             |

| Operating temperature | Topr   | -20     | 70      | ${\mathbb C}$ |

| Storage temperature   | Tstr   | -30     | 80      | $^{\circ}$    |

### 7. ELECTRICAL CHARACTERISTICS.

| Item                |         | Symbol           | Condition | Min             | Тур. | Max.            | Unit       |

|---------------------|---------|------------------|-----------|-----------------|------|-----------------|------------|

| Supply Vo           | ltage   | Logic            | Vdd-GND   | -               | 3.0  | -               | V          |

| Input<br>voltage    | H level | $V_{DD}$         |           | $0.8V_{\rm DD}$ | -    | $V_{DD}$        | <b>X</b> 7 |

|                     | L level | VIH              | -         | Vss             | -    | $0.2V_{\rm DD}$ | V          |

| LCD Driving Voltage |         | V <sub>LCD</sub> |           | -               | 10.3 | -               | V          |

Note1. The value is measure at following condition; follow same condition to test sample and mass product.

(a)VDD=3.0V (b)1/65Duty,1/9Bias

#### 8. MODULE FUNCTION DESCRIPTION

# 1. Timing Characteristics

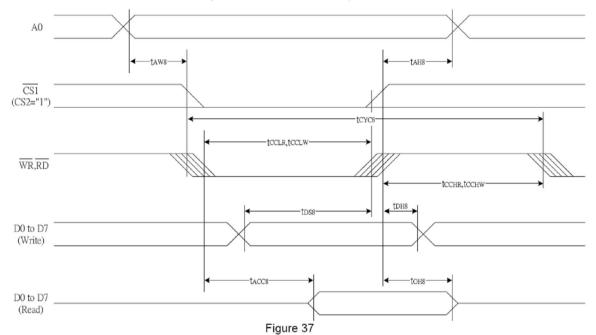

System Bus Read/Write Characteristics 1 (For the 8080 Series MPU)

(VDD = 3.3V , Ta =25°C)

| Itom                         | Cianal     | Cumbal           | Condition   | Rating |      | Units |

|------------------------------|------------|------------------|-------------|--------|------|-------|

| Item                         | Signal     | Symbol           | Condition   | Min.   | Max. | Units |

| Address hold time            |            | tah8             |             | 0      | _    |       |

| Address setup time           | A0         | taw8             |             | 0      | _    |       |

| System cycle time            |            | tcyc8            |             | 240    | _    |       |

| Enable L pulse width (WRITE) | WR         | toclw            |             | 80     | _    |       |

| Enable H pulse width (WRITE) |            | tcchw            |             | 80     | _    |       |

| Enable L pulse width (READ)  | RD         | tcclr            |             | 140    | _    | Ns    |

| Enable H pulse width (READ)  | , KD       | tcchr            |             | 80     |      |       |

| WRITE Data setup time        |            | tDS8             |             | 40     | _    |       |

| WRITE Address hold time      | D0 to D7   | t <sub>DH8</sub> |             | 0      | _    |       |

| READ access time             | י טט וט טי | tACC8            | CL = 100 pF | _      | 70   | ]     |

| READ Output disable time     | Ī          | toн8             | CL = 100 pF | 5      | 50   | 1     |

$(VDD = 2.7 V, Ta = 25^{\circ}C)$

| Item                         | Signal   | Symbol | Condition   | Rat  | ing  | Units |

|------------------------------|----------|--------|-------------|------|------|-------|

| item                         | Signai   | Symbol | Condition   | Min. | Max. | Onits |

| Address hold time            |          | tan8   |             | 0    | _    |       |

| Address setup time           | A0       | taw8   |             | 0    | _    |       |

| System cycle time            |          | tcyc8  |             | 400  | _    |       |

| Enable L pulse width (WRITE) | WR       | tccLw  |             | 220  | _    |       |

| Enable H pulse width (WRITE) |          | tccнw  |             | 180  | _    |       |

| Enable L pulse width (READ)  | RD       | tcclr  |             | 220  | _    | ns    |

| Enable H pulse width (READ)  | IND.     | tcchr  |             | 180  | _    |       |

| WRITE Data setup time        |          | tDS8   |             | 40   | _    |       |

| WRITE Address hold time      | D0 to D7 | tDH8   |             | 0    | _    |       |

| READ access time             | 201017   | taccs  | CL = 100 pF | _    | 140  |       |

| READ Output disable time     |          | ton8   | CL = 100 pF | 10   | 100  |       |

(VDD = 1.8V . Ta = 25°C )

|                              |          |                  |             |        |      | ( )   |

|------------------------------|----------|------------------|-------------|--------|------|-------|

| Item                         | Signal   | Symbol           | Condition   | Rating |      | Units |

| Item                         | Signal   | Syllibol         | Condition   | Min.   | Max. | Units |

| Address hold time            | i c      | tah8             |             | 0      | _    |       |

| Address setup time           | Α0       | taw8             |             | 0      | _    |       |

| System cycle time            | f        | tcyc8            |             | 640    | _    |       |

| Enable L pulse width (WRITE) | WR       | tcclw            |             | 360    | _    | ]     |

| Enable H pulse width (WRITE) |          | tcchw            |             | 280    | _    |       |

| Enable L pulse width (READ)  | RD       | tcclr            |             | 360    | _    | ns    |

| Enable H pulse width (READ)  | , KD     | tcchr            |             | 280    |      |       |

| WRITE Data setup time        |          | tDS8             |             | 80     | _    | 1     |

| WRITE Address hold time      | D0 to D7 | t <sub>DH8</sub> |             | 0      | _    | ]     |

| READ access time             | D0 to D7 | tacc8            | CL = 100 pF | _      | 240  | 1     |

| READ Output disable time     |          | toн8             | CL = 100 pF | 10     | 200  | 1     |

<sup>\*1</sup> The input signal rise time and fall time (tr, tr) is specified at 15 ns or less. When the system cycle time is extremely fas (tr +tr)  $\leq$  (tcyc8 – tccLw – tccHw) for (tr + tr)  $\leq$  (tcyc8 – tccLR – tccHR) are specified. \*2 All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3</sup> tocum and tocur are specified as the overlap between /CS1 being "L" (CS2 = "H") and /WR and /RD being at the "L" leve

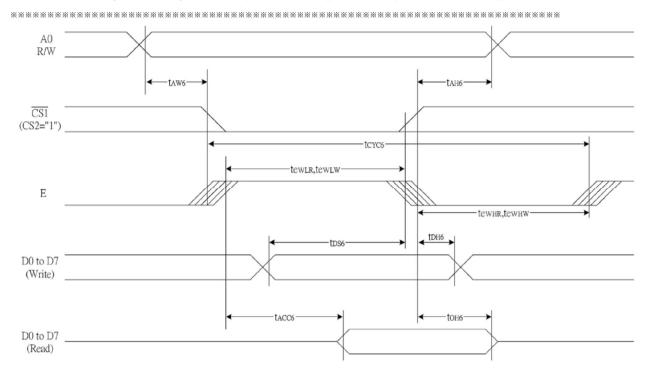

#### System Bus Read/Write Characteristics 2 (For the 6800 Series MPU)

Figure 38

Table 27

|                              |          | _            |             | (VDD = 3.3) | V , Ta = 25 | °C)   |

|------------------------------|----------|--------------|-------------|-------------|-------------|-------|

| Item                         | Signal   | Symbol       | Condition   | Rating      |             | Units |

| item                         |          | Symbol       | Condition   | Min.        | Max.        | Omits |

| Address hold time            |          | tah6         |             | 0           | _           |       |

| Address setup time           | A0       | tAW6         |             | 0           | _           |       |

| System cycle time            |          | tcyc6        |             | 240         | _           |       |

| Enable L pulse width (WRITE) | WR       | tewlw        |             | 80          | _           |       |

| Enable H pulse width (WRITE) |          | tewhw        |             | 80          | _           |       |

| Enable L pulse width (READ)  | RD       | tewlr        |             | 80          | _           | ns    |

| Enable H pulse width (READ)  | , KD     | tewhr        |             | 140         |             |       |

| WRITE Data setup time        |          | tDS6         |             | 40          | _           |       |

| WRITE Address hold time      | D0 to D7 | tDH6         |             | 0           | _           |       |

| READ access time             | D0 to D7 | tACC6        | CL = 100 pF | _           | 70          |       |

| READ Output disable time     |          | <b>t</b> он6 | CL = 100 pF | 5           | 50          |       |

\*\*\*\*\*

(VDD = 2.7V , Ta =25°C )

| Item                         | Gianal   | Signal Symbol Condition |             | Rat  | Units |        |

|------------------------------|----------|-------------------------|-------------|------|-------|--------|

| Item                         | Signai   | Symbol                  | Condition   | Min. | Max.  | Ullits |

| Address hold time            |          | <b>t</b> AH6            |             | 0    | _     |        |

| Address setup time           | A0       | tAW6                    |             | 0    | _     |        |

| System cycle time            |          | tcyc6                   |             | 400  | _     |        |

| Enable L pulse width (WRITE) | WR       | tewlw                   |             | 220  | _     |        |

| Enable H pulse width (WRITE) | VVIX     | tewnw                   |             | 180  | _     |        |

| Enable L pulse width (READ)  | RD       | tewlr                   |             | 220  | _     | ns     |

| Enable H pulse width (READ)  | , KD     | <b>t</b> EWHR           |             | 180  | _     |        |

| WRITE Data setup time        |          | tDS6                    |             | 40   | _     |        |

| WRITE Address hold time      | D0 to D7 | tDH6                    |             | 0    | _     |        |

| READ access time             |          | tACC6                   | CL = 100 pF | _    | 140   |        |

| READ Output disable time     |          | <b>t</b> он6            | CL = 100 pF | 10   | 100   |        |

#### Table 29

(VDD =1.8V , Ta =25°C)

| Item                         | Cianal   | Signal Symbol Condition |             | Rat  | Units |        |

|------------------------------|----------|-------------------------|-------------|------|-------|--------|

| iteiii                       | Signal   | Symbol                  | Condition   | Min. | Max.  | Ullits |

| Address hold time            |          | tah6                    |             | 0    | _     |        |

| Address setup time           | A0       | taw6                    |             | 0    | _     |        |

| System cycle time            |          | tcyc6                   |             | 640  | _     |        |

| Enable L pulse width (WRITE) | WR       | tewlw                   |             | 360  | _     |        |

| Enable H pulse width (WRITE) | VVIX     | tewnw                   |             | 280  | _     |        |

| Enable L pulse width (READ)  | RD       | tewlr                   |             | 360  | _     | ns     |

| Enable H pulse width (READ)  | אט       | <b>t</b> EWHR           |             | 280  | _     |        |

| WRITE Data setup time        |          | tDS6                    |             | 80   | _     |        |

| WRITE Address hold time      | D0 to D7 | tDH6                    |             | 0    | _     |        |

| READ access time             | 00 10 07 | tACC6                   | CL = 100 pF | _    | 240   |        |

| READ Output disable time     |          | <b>t</b> он6            | CL = 100 pF | 10   | 200   |        |

<sup>\*1</sup> The input signal rise time and fall time  $(t_r, t_f)$  is specified at 15 ns or less. When the system cycle time is extremely fast,  $(t_r + t_f) \le (t_{CYC6} - t_{EWLW} - t_{EWHW})$  for  $(t_r + t_f) \le (t_{CYC6} - t_{EWLR} - t_{EWHR})$  are specified.

<sup>\*2</sup> All timing is specified using 20% and 80% of VDD as the reference.

<sup>\*3</sup> tewlw and tewlr are specified as the overlap between CS1 being "L" (CS2 = "H") and E.

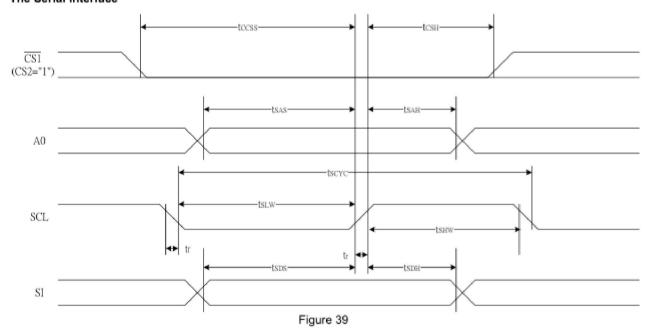

#### The Serial Interface

Table 30

(VDD = 3.3V, Ta =25°C)

|                     |        |                         |           | ( V DD - 5.0 | )v, ra –25 | ~ /   |  |

|---------------------|--------|-------------------------|-----------|--------------|------------|-------|--|

| Item                | Signal | Signal Symbol Condition |           | Rati         | Units      |       |  |

| item                | Signal | Symbol                  | Condition | Min.         | Max.       | Onits |  |

| Serial Clock Period |        | Tscyc                   |           | 100          | _          |       |  |

| SCL *H" pulse width | SCL    | Tshw                    |           | 50           | _          | ]     |  |

| SCL "L" pulse width |        | Tslw                    |           | 50           | _          |       |  |

| Address setup time  | A0     | Tsas                    |           | 20           | _          |       |  |

| Address hold time   | 7 40   | Tsah                    |           | 10           | _          | ns    |  |

| Data setup time     | SI     | Tsds                    |           | 20           | -          | 1     |  |

| Data hold time      | 7 31   | TspH                    |           | 10           | _          | ]     |  |

| CS-SCL time         | cs     | Tcss                    |           | 20           | _          | ]     |  |

| CS-SCL time         | 7 6    | Tcsh                    |           | 40           | _          |       |  |

Table 31

(VDD =2.7V, Ta =25°C)

| Item                | Signal | Symbol   | Condition | Rating |      | Units  |

|---------------------|--------|----------|-----------|--------|------|--------|

| item                | Signal | Syllibol | Condition | Min.   | Max. | Ullits |

| Serial Clock Period |        | Tscyc    |           | 120    | _    |        |

| SCL "H" pulse width | SCL    | Tshw     |           | 60     | _    |        |

| SCL "L" pulse width |        | Tstw     |           | 60     | _    | ]      |

| Address setup time  | A0     | Tsas     |           | 30     | _    |        |

| Address hold time   | Αυ     | Тѕан     |           | 20     | _    | ns     |

| Data setup time     | SI     | Tsps     |           | 30     | _    |        |

| Data hold time      | 31     | Тѕрн     |           | 20     | _    |        |

| CS-SCL time         | cs     | Tcss     |           | 30     | _    | ]      |

| CS-SCL time         |        | Тсѕн     |           | 60     | _    |        |

#### 2. APPLICATION OF LCM

#### 3.COMMAND TABLE

| Commond                                                                |    |     |     |    | Com | mano | i Cod       | le          |            |               |              | Frankling                                                                                                                                         |  |

|------------------------------------------------------------------------|----|-----|-----|----|-----|------|-------------|-------------|------------|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Command                                                                | Α0 | /RD | /WR | D7 | D6  | D5   | D4          | D3          | D2         | D1            | D0           | Function                                                                                                                                          |  |

| (1) Display ON/OFF                                                     | 0  | 1   | 0   | 1  | 0   | 1    | 0           | 1           | 1          | 1             | 0            | LCD display ON/OFF<br>0: OFF, 1: ON                                                                                                               |  |

| (2) Display start line set                                             | 0  | 1   | 0   | 0  | 1   |      | Displ       | ay st       | art a      | ddre:         | ss           | Sets the display RAM display start line address                                                                                                   |  |

| (3) Page address set                                                   | 0  | 1   | 0   | 1  | 0   | 1    | 1           | Р           | age        | addr          | ess          | Sets the display RAM page address                                                                                                                 |  |

| (4) Column address set<br>upper bit<br>Column address set<br>lower bit | 0  | 1   | 0   | 0  | 0   | 0    | 1<br>0      | co<br>Le    |            | add<br>ignifi | ress<br>cant | Sets the most significant 4 bits of the display<br>RAM column address.<br>Sets the least significant 4 bits of the display<br>RAM column address. |  |

| (5) Status read                                                        | 0  | 0   | 1   |    | Sta | itus |             | 0           | 0          | 0             | 0            | Reads the status data                                                                                                                             |  |

| (6) Display data write                                                 | 1  | 1   | 0   |    |     |      |             | W           | rite d     | ata           |              | Writes to the display RAM                                                                                                                         |  |

| (7) Display data read                                                  | 1  | 0   | 1   |    |     |      |             | Re          | ad d       | ata           |              | Reads from the display RAM                                                                                                                        |  |

| (8) ADC select                                                         | 0  | 1   | 0   | 1  | 0   | 1    | 0           | 0           | 0          | 0             | 0            | Sets the display RAM address SEG output correspondence 0: normal, 1: reverse                                                                      |  |

| (9) Display normal/<br>reverse                                         | 0  | 1   | 0   | 1  | 0   | 1    | 0           | 0           | 1          | 1             | 0            | Sets the LCD display normal/ reverse<br>0: normal, 1: reverse                                                                                     |  |

| (10) Display all points<br>ON/OFF                                      | 0  | 1   | 0   | 1  | 0   | 1    | 0           | 0           | 1          | 0             | 0<br>1       | Display all points<br>0: normal display<br>1: all points ON                                                                                       |  |

| (11) LCD bias set                                                      | 0  | 1   | 0   | 1  | 0   | 1    | 0           | 0           | 0          | 1             | 0<br>1       | Sets the LCD drive voltage bias ratio 0: 1/9 bias, 1: 1/7 bias (ST7565R)                                                                          |  |

| (12) Read-modify-write                                                 | 0  | 1   | 0   | 1  | 1   | 1    | 0           | 0           | 0          | 0             | 0            | Column address increment<br>At write: +1<br>At read: 0                                                                                            |  |

| (13) End                                                               | 0  | 1   | 0   | 1  | 1   | 1    | 0           | 1           | 1          | 1             | 0            | Clear read/modify/write                                                                                                                           |  |

| (14) Reset                                                             | 0  | 1   | 0   | 1  | 1   | 1    | 0           | 0           | 0          | 1             | 0            | Internal reset                                                                                                                                    |  |

| (15) Common output<br>mode select                                      | 0  | 1   | 0   | 1  | 1   | 0    | 0           | 0           | *          | *             | *            | Select COM output scan direction<br>0: normal direction<br>1: reverse direction                                                                   |  |

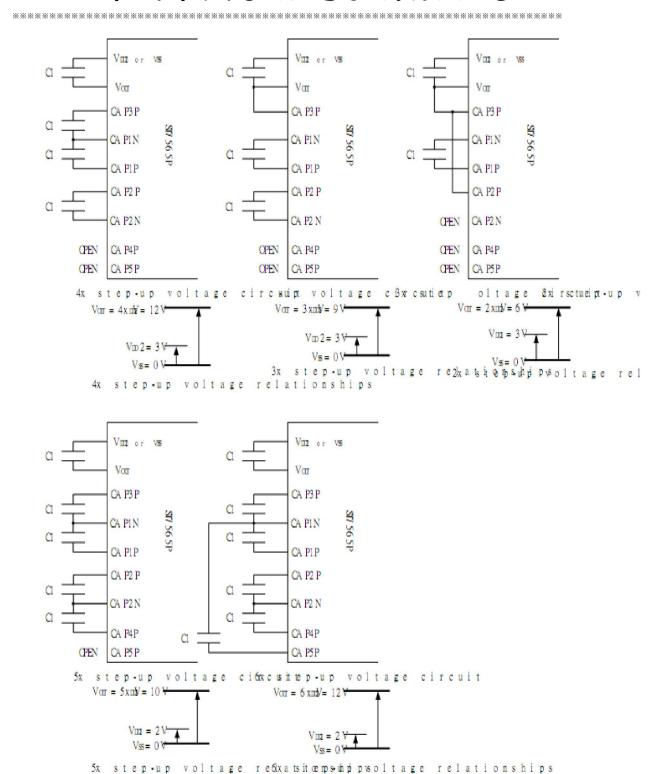

| (16) Power control set                                                 | 0  | 1   | 0   | 0  | 0   | 1    | 0           | 1           | 0          | pera<br>mod   |              | Select internal power supply operating mode                                                                                                       |  |

| (17) V₀ voltage<br>regulator internal<br>resistor ratio set            | 0  | 1   | 0   | 0  | 0   | 1    | 0           | 0           | Res        | sistor        | ratio        | Select internal resistor ratio(Rb/Ra) mode                                                                                                        |  |

| (18) Electronic volume<br>mode set<br>Electronic volume                | 0  | 1   | 0   | 1  | 0   | 0    | 0<br>lectro | 0<br>onic v | 0<br>volun | 0<br>ne va    | 1<br>ilue    | Set the V₀ output voltage electronic volume register                                                                                              |  |

| register set<br>(19) Static indicator<br>ON/OFF                        | 0  |     | 0   | 1  | 0   | 1    | 0           | 1           | 1          | 0             | 0            | 0: OFF, 1: ON                                                                                                                                     |  |

| Static indicator<br>register set                                       | U  | 1   | U   | 0  | 0   | 0    | 0           | 0           | 0          | 0             | 1<br>Mode    | Set the flashing mode                                                                                                                             |  |

| (20) Beaster sette                                                     | _  |     |     | 1  | 1   | 1    | 1           | 1           | 0          | 0             | 0            | select booster ratio<br>00: 2x,3x,4x                                                                                                              |  |

| (20) Booster ratio set                                                 | 0  | 1   | 0   | 0  | 0   | 0    | 0           | 0           | 0          |               | p-up<br>alue | 01: 5x<br>11: 6x                                                                                                                                  |  |

| (21) Power save                                                        | 0  | 1   | 0   |    |     |      |             |             |            |               |              | Display OFF and display all points ON compound command                                                                                            |  |

| (22) NOP                                                               | 0  | 1   | 0   | 1  | 1   | 1    | 0           | 0           | 0          | 1             | 1            | Command for non-operation                                                                                                                         |  |

| (23) Test                                                              | 0  | 1   | 0   | 1  | 1   | 1    | 1           | *           | *          | *             | *            | Command for IC test. Do not<br>use this command                                                                                                   |  |

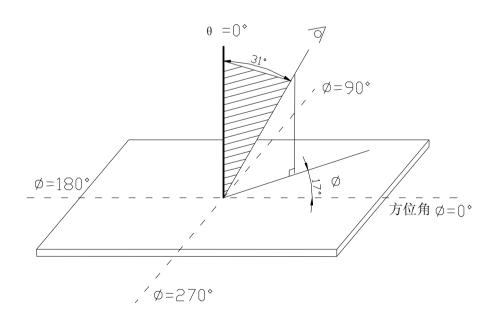

# 9. Electro-Optical Characteristics

#### (1). STN Type

| Item     | Symbol           | Condition | Min                        | Тур | Max | Units |

|----------|------------------|-----------|----------------------------|-----|-----|-------|

| Contrast | K                | θ=0° Φ=0° | 5: 1                       |     |     | deg.  |

| Viewing  | 0                | К=5 Ф=0°  | $\theta_2 - \theta_1 = 30$ |     |     | deg.  |

| Angle    | θ                | K=5 θ=10° | $\Phi = \pm 30$            |     |     | deg.  |

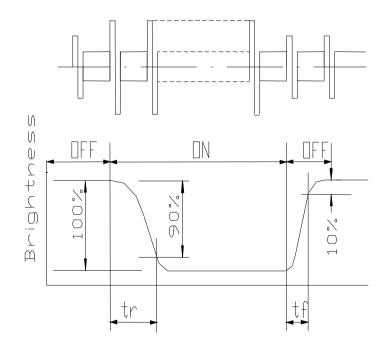

| Response | Ton              | 25°C      | _                          |     | 250 | ms    |

| time     | T <sub>off</sub> | 25°C      |                            |     | 250 | ms    |

#### (2). Definition of Optical Response Time

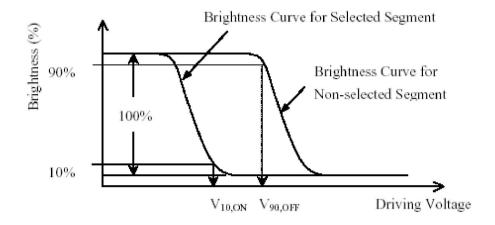

#### (3). Definition of Driving Voltage (Vlcd)

$$Vlcd = (V_{10,ON} + V_{90,OFF})/2$$

#### (4). Definition of Viewing Angle $\theta$ and $\Phi$